Tampon de réorganisation

Un tampon de réorganisation (en anglais : Re-order buffer ou ROB) est une unité matérielle du coeur d'un microprocesseur utilisée dans une extension de l’algorithme de Tomasulo pour prendre en charge l’exécution d’instructions dans le désordre et spéculatives. L’extension force les instructions à être validées dans l’ordre.

Le tampon est un buffer circulaire (de type FIFO, pour fournir une file d'attente de classement des instructions) implémenté sous forme de tableau/vecteur (qui permet d’enregistrer les résultats des instructions lorsqu’elles se terminent dans le désordre).

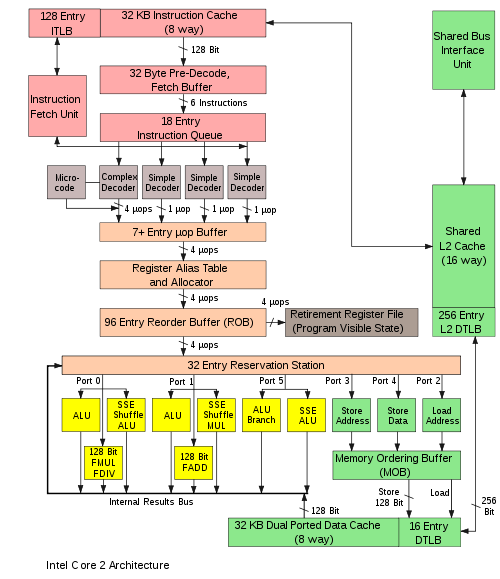

L’algorithme de Tomasulo se déroule en trois étapes : « Issue » (émettre l'instruction), « Execute » (exécuter l'instruction), « Write Result » (écrire le résultat). Dans une extension de l’algorithme, il existe une étape supplémentaire « Commit » (validation). Au cours de l’étape « Commit », les résultats des instructions sont stockés dans un registre ou une mémoire. L’étape « Write Result » est modifiée pour placer les résultats dans le tampon de réorganisation. A cet effet, chaque instruction est étiquetée dans la station de réservation (en) avec son index dans le ROB.

Le contenu de la mémoire tampon est utilisé pour les dépendances de données d’autres instructions planifiées dans la mémoire tampon. La tête du tampon sera validée une fois que son résultat sera valide. Ses dépendances auront déjà été calculées et validées puisqu’elles doivent être en avance sur l’instruction dans le tampon, mais pas nécessairement adjacentes à celle-ci. Les dépendances de données entre les instructions bloquent normalement le pipeline pendant qu’une instruction attend ses valeurs dépendantes. Le ROB permet au pipeline de continuer à traiter d’autres instructions tout en s’assurant que les résultats sont validés afin d’éviter les risques de données corrompues tels que la lecture avant écriture (RAW), l’écriture avant lecture (WAR) et l’écriture avant écriture (WAW).

Il existe des champs supplémentaires dans chaque entrée de la mémoire tampon pour prendre en charge l’algorithme étendu :

- Type d’instruction (saut, stockage en mémoire, stockage en registre)

- Destination (adresse mémoire ou numéro de registre)

- Résultat (valeur qui va à la destination ou indication d’un saut réussi/non réussi)

- Validité (le résultat existe-t-il déjà ?)

La mémoire tampon de réorganisation permet également un contrôle précis des exceptions et de la restauration des prédictions erronées de l'adresse cible (branchement ou saut). Lorsque la prédiction du saut n’est pas correcte ou qu’une exception non récupérable est rencontrée dans le flux d’instructions, le ROB est effacé de toutes les instructions (en faisant pointer la queue de la file d’attente circulaire sur la tête) et les stations de réservation sont réinitialisées.

Références

modifierLiens externes

modifier- (en) « Hardware Based Speculation - Prof. Dr. Ben H. Juurlink (vidéo) » (consulté le )

- (en) « Reorder Buffer » (consulté le )